電子部品 - FPGA

概要

FPGAとは、デバイス内部の電子制御機能の大部分を変更できる半導体ICのことである。

FPGAは、電源を投入することにより、その変更した機能で動作させることができる。

したがって、設計者は、新しい構成ファイルをデバイスにダウンロードして変更内容を試すだけで、容易に設計変更を行うことができる。

変更は、設計段階、プリント基板のアセンブリプロセス中、機器が顧客へ出荷された後の現場等で行うことができる。

多くの場合、FPGAの回路構成を変更する際は、プリント基板側に変更を加える必要がないため、コストを節約できる。

ASSP(特定用途向け大規模集積回路)やASIC(完全カスタム大規模集積回路)は、ハードウェア機能が固定されているため、

変更を行うには、ASSPやASICそのものの置き換えに加えて、プリント基板の再設計等、多大なコストと時間が必要になる。

また、ASICが回路設計から量産まで最低でも数カ月を要するのに対し、FPGAとASSPは汎用品として販売されているので、すぐに製品に組み込むことができる。

FPGAの方式

FPGAは、SRAMメモリセル方式が主流であるが、それ以外にも様々な方式のFPGAが存在する。

1980年代後半、ヒューズ方式(アンチヒューズFPGA)が登場した。

ヒューズ方式は、回路の接点がヒューズになっており、ヒューズを焼き切ることで回路を形成する。

アンチヒューズ素子は、1度だけプログラム可能な記憶素子であり、プログラムすれば低抵抗で導通する。

また、SRAM素子より小さいため高集積が可能であり、低抵抗で高速に動作できる。

ただし、高価であり、書き換えは不可能なため何度も繰り返して使用できない。

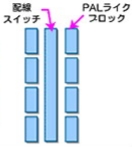

同時期に、CPLD(Complex PLD)が登場しており、複数個の小規模なPLDを1個のLSIに集積することにより、任意の大規模論理回路を実現できる。

小規模PLDと同様、不揮発であり書き換えが可能という特徴がある。

ただし、設計自由度の高さではFPGAに及ばない。

1990年代には、Flash ROM技術を用いたFlash FPGAが登場した。

Flash FPGAは、書き換え可能というSRAM方式の利点と、不揮発性というアンチヒューズFPGAの利点を兼ね備えている。

しかし、その構造と製造プロセスの複雑さから、集積度を引き上げること、低価格化が困難なため、

大容量・高速動作が要求されるFPGAにはあまり使用されなかった。

現在の主流は、高速・大規模な場合はSRAMメモリセル方式のFPGA、高速性や規模が必要でない場合はCPLDである。

両者とも、その構造上、製造性がよく安価である。

| PAL(Simple PLD) | CPLD(Complex PLD) | FPGA | |

|---|---|---|---|

| 論理ソース | 少量 小さな論理セル |

少量 大きな論理ブロック |

多量 大きな論理ブロック |

| 配線 | 固定減算構成 | スイッチ・マトリクス構造 | グローバル / ローカル加算型構成 |

| タイミング | 超構成 固定 |

高速 固定 |

配置・配線結果による |

| デザイン処理 | 事前予測可能 | 事前予測可能 | 高度で複雑 |

| ソフトウェアの作業 | コンパイル フィッティング |

コンパイル フィッティング |

配置・配線 シミュレーション インシステムアナライザ |

| プログラム技術 | Flash EPROM EEPROM |

Flash EPROM EEPROM |

Flash SRAM アンチヒューズ |

FPGAの仕組み

まず、論理回路の基になるプログラムについて記載する。

FPGAのプログラムは、SRAMメモリセル型の場合は、外部記憶デバイスであるFlash ROMやEEPROM等に記録されている。

SRAMメモリセル型のFPGAに電源が投入されると、外部記憶デバイスからプログラムファイルがロードされる。

このプログラムファイルのことを、ビットストリームデータと呼ぶ。

この情報は、FPGA内部にある1ビット列のSRAMメモリセルで構成されているコンフィグレーションメモリにロードされる。

ロードされたビットストリームデータの個々のビットが、FPGA上で実現する論理回路の基となり、

FPGAに装備されているリソースをカスタマイズしてユーザ所望の回路を実現する。

これは、PCにおけるCPUのブートプロセスと非常によく似ている。

ハードウェアに依存せず、コンフィグレーションデータを外部に持つことで、高い汎用性とフレキシビリティを実現している。

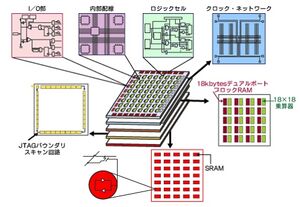

次に、FPGAの内部構造について記載する。

FPGAの内部構造は、以下の6つの部分に大別できる。(下図を参照)

- I/O部

- 内部配線

- ロジックセル

- クロックネットワーク

- JTAGバウンダリスキャン回路

- Block RAM・乗算器

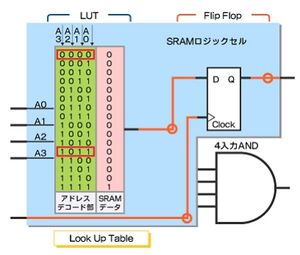

ロジックセルは、一般的に、4入力または6入力のルックアップテーブル(LUT)とフリップフロップの2つから構成される。

SRAMメモリセルのアドレスに当たる部分に信号が入力される時、その組み合わせに応じて、LUTに記憶されているデータを出力する。

下図は、AND回路として使用する場合を示す。

全てのアドレスが1になる部分にHighのデータ、それ以外にはLowのデータが書き込まれている。

そこで入力が全て1の時、データとして保持されている1が出力される。

その後、フリップフロップにより、システムに同期したタイミングでデータが出力される。

ロジックセルは、FPGAの全面に分散して配置されており、これらを内部配線で自動接続することによりユーザの求めるファンクションを実現する。

なお、ロジックセルのLUTは、ロジックの実現だけでなく、小型のメモリ(4入力のLUTは16[bit]メモリ)としても使用できる。

したがって、Block RAM以外にも局所的にメモリを増やすことができる。(この状態のLUTを分散型メモリと呼ぶ)

I/O部は、主にFPGAの周辺部に位置しており、外部信号のやりとりを行う。

現在では、20種類を超える様々な電圧レベルや規格に対応できるフレキシブルなI/Oが提供されており、自由にボード上の配線を実現できる。

内部配線は、ロジックセル間やI/O部を結合して、ユーザの求めるファンクションを実現する。

クロックネットワークは、FPGA内部のクロックを配分するためのリソースである。

FPGA全体に供給するクロックと、局所的に使用するクロックの2種類が提供されており、各所で最適な回路動作を実現する。

特に、クロックネットワークは同期回路の設計に必須である。

JTAGバウンダリスキャン回路は、デバッグ試験のための機能を提供する。

Block RAM・乗算器は、論理を実現するためのリソースである。

上図(FPGAアーキテクチャ概念図)のように、回路全体に対して、均一的にBlock RAM・乗算器が提供されることで、

ユーザはFPGA内部での回路の位置に制限を受けることなく、演算処理とデータの保持ができる。

以上、記載した6つのリソースが1つのシリコンの上に組み込まれることで、FPGA内部の回路配置の制限をほぼ受けることなく、

希望するファンクションを実現できる。

FPGAのデザイン手順

一般的な開発環境は、各ベンダおよびサードパーティから提供されている。

論理合成ツールとレイアウトツールが主なツールである。

FPGAの論理設計は、VHDLまたはVerilog HDLで設計するケースが多い。

そのため、仕様の段階でハードウェアとソフトウェアの処理を分断して、ハードウェアはHDL、ソフトウェアはC言語と分けて設計する。

しかし、プロセッサやDSPがFPGA内部で実現可能なので、ハードウェアとソフトウェアの協調設計が必要となる。

統一した言語(例 : C言語)等でハードウェアとソフトウェアを含めた記述をした後、最適な作業の振り分けを行うツールが重要であり、

ハードウェアベンダとソフトウェアベンダが協調して、新しいシステムレベルでの開発環境ツールを提供している。

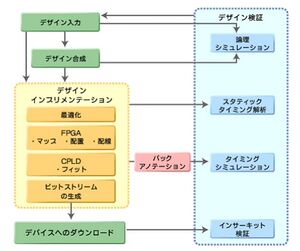

下図に、FPGAのデザインフローを示す。

まず、HDL等の言語でデザインを記述して、論理合成ツールを使用してデザイン合成する。

この時、論理シミュレーションを使用してデザイン検証を行う。

次に、デザインインプリメンテーションを実施する。

これは、FPGA内部に論理回路を組み込む作業である。

各ファンクションをロジックセル上でどのように実現するのが最も効率的か(最適化)、

それをFPGA内部でどのように配置・配線するか(配置配線)を行うことで、FPGA内部での配置が具体的に決まる。

この時、高速動作する論理回路では、スタティックタイミング解析やタイミングシミュレーションを行い、期待するタイミングで動作するかを検証する。

特に、動作周波数を限界近くで使用する場合等は、ロジックセル間を繋ぐ配線の遅延等が要因でタイミング遅延が発生するので確認が必要である。

事前に、タイミングがクリティカルな場所が判別できる場合は、ツール上で制約を与えてインプリメンテーションすることが可能である。

ツール上において、デザインが仕様通り動作することを確認する。

次に、プログラムを書き込むために必要なビットストリームファイルを作成して、FPGAの外部記憶デバイスにダウンロードする。

つまり、JTAG等を用いて、ビットストリームファイルをシステム上の外部記憶デバイスに書き込む。

最後に、実機上での試験を実施する。

実際のシステムでは、FPGA以外の回路やデバイスと連携・動作するため、実機での検証・インサーキット検証を必ず実施する。