マイコンの基礎 - メモリ増設

概要

メモリの外部拡張機能のあるマイコンであれば、簡単にメモリを増設することができる。

また、増設したメモリは、マイコンから見る場合は、マイコンのメモリ領域に拡張される形で扱うことができる。

しかし、メモリの外部拡張機能はマイコンによって異なるため、ここでは、STM32F7シリーズのSTM32F7x5を例に記載する。

STM32F7x5は、外部メモリに簡単にアクセスできるフレキシブルメモリコントローラ(以下、FMCという)が搭載されている。

FMCを使用すると、外部にPSRAM、NORフラッシュ、NANDフラッシュ、同期DRAM等が接続できる。

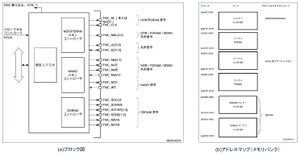

下図に、FMCのブロック図(図(a))とアドレスマップ(図(b))を示す。

アドレス空間内に4つのバンクを持ち、バンク1はNORフラッシュ / PSRAM / SRAM、バンク3はNANDフラッシュ、SDRAMバンク1と2はSDRAMに対応している。

各アドレス範囲は、下図(b)の通りである。

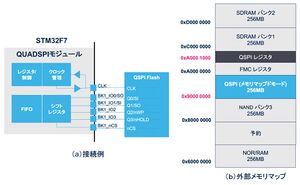

Quad SPIインタフェース(以下、QSPIという)を持つ外部メモリであれば、STM32F7x5のQSPIモジュールを使用して接続できる。

QSPIのメモリマップドモードを使用すると、外部メモリはアドレス空間(0x90000000台)に配置され、内部メモリであるかのようにみなされる。

QSPIの詳細は、マイコンの基礎 - Quad SPIを参照すること。

メモリの外部拡張機能

多くのマイコンにメモリの外部拡張機能が搭載されており、その仕様や名称、使用方法等はマイコンによって異なる。

したがって、各マイコンのマニュアルやアプリケーションノートを参照する必要がある。

ここでは、STM32F7シリーズのSTM32F745を例に記載する。

STM32F745には、Arm Cortex-M7(以下、Cortex-M7という)が搭載されている。

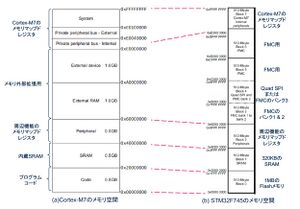

下図(a)に示すように、Cortex-M7の扱えるメモリ空間は0x00000000~0xFFFFFFFFの4[GB]だが、実際のマイコンに4[GB]のメモリを搭載することは不可能である。

そこで、ターゲットとするマイコンをベースとした必要最低限の実メモリを搭載する。

例えば、STM32F745ではフラッシュメモリを1[MB]、SRAMを320[KB]搭載している。

しかし、システムを開発する上で、ファームウェアのサイズが予定よりも大きくなったり、RAM領域が不足する場合がある。

このような場合、メモリの外部拡張機能を使用して、プログラムコード領域やRAM領域を増設できる。

下図(a)に、Cortex-M7オリジナルのメモリ空間を示す。

各領域は、0.5[GB]または1[GB]で区切られており、

アドレスの小さい方から、0.5[GB]ごとにプログラムコード用、内蔵SRAM用、周辺機能のメモリマップドレジスタ用となっている。

最も大きな領域はCortex-M7専用の領域になっており、その間のアドレス0x60000000~0xDFFFFFFFがメモリの外部拡張機能用に割り当てられている。

それぞれ、外部RAM用と外部デバイス用に1[GB]単位で区切られている。

※FSMC(フレキシブル静的メモリコントローラ)

STM32の外部にSRAM / フラッシュメモリ / LCD等を接続するための機能である。

STM32F745では、この外部拡張機能用の領域を、FMC用とQSPI用に割り当てている。

FMCの扱うアドレス空間内は全部で6個のバンクあるが、その内2個のバンクは使用されていないため、有効なバンクは4個となる。

バンク1はNORフラッシュ / PSRAM / SRAM、バンク3はNANDフラッシュ(QSPIと共用)、SDRAMバンク1と2はSDRAMにそれぞれ対応している。

FMCを使用して外部のSRAMにアクセスする場合、バンク1に割り当てられている0x60000000~0x6FFFFFFFに外部のSRAMが見える。

外部に接続された単体のSRAMのアドレスは0x000から始まり、実際には0x60000000台ではないが、

FMCがアドレス変換を行い、マイコンから見ると仮想的に0x60000000台に配置される。

また、QSPIを使用した場合は、0x90000000台に配置される。

FMC(フレキシブルメモリコントローラ)

下図に、"メモリの外部拡張機能"セクションの図に掲載したSTM32F745のFMCのブロック図を再掲する。

FMCは、以下のブロックで構成されている。

※AHB(Advanced High-performance Bus)とは、マイコンの内部バスである。

- 設定レジスタ(AHBインタフェースを含む)

- NORフラッシュ / PSRAMメモリコントローラ

- NANDフラッシュメモリコントローラ

- SDRAMコントローラ

FMCは、マイコンの内部バスと外部デバイスの間に位置しており、インタフェースの役割を果たしている。

具体的には、外部デバイスのプロトコルを内部バスのプロトコルに変換して、外部デバイスがマイコン内部に存在するかのように動作させる。

FMCの主な機能は、以下の通りである。

- 外部デバイス(同期 / 非同期)とのインタフェース

- 同期外部デバイスに対するアクセスを高速化するバーストモードのサポート

- 非同期アクセスと同期アクセス用のプログラム可能な連続クロック出力

- 8ビット / 16ビット / 32ビット幅のデータバス

- 各メモリバンクに対する独立したチップセレクト制御

- メモリバンクごとに独立した設定

- 書き込みイネーブルとバイトレーン選択出力

- 外部非同期ウェイト制御

- 16×32ビットの深さの書き込みFIFO

- キャッシュ可能読み出しFIFO

FMCの仕様と使用方法の詳細は、アプリケーションノートを参照すること。

FMC使用例1 : 非多重 / 非同期16ビットNORフラッシュとの接続

NORフラッシュを制御するために、FMCをNORフラッシュの仕様にしたがって設定する。

以下に、FMCの設定例を示す。

また、他のパラメータは、全てクリア状態にする。

- バンクは、NORフラッシュを選択

- バンクを許可

- メモリタイプはNORフラッシュを選択

- データバスを16ビットに設定

- 非多重メモリを選択

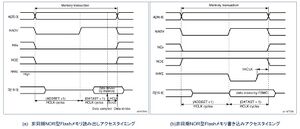

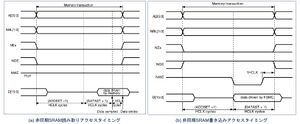

下図に、NORフラッシュのアクセスタイミングを示す。

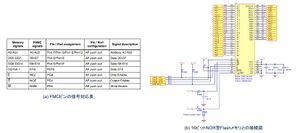

下図に、ハードウェアの接続例を示す。

NORフラッシュ / PSRAMコントローラは、非同期 / 同期メモリ双方のサポートが可能である。

そのため、ユーザはメモリの仕様にしたがって使用するパラメータを設定する。

非同期メモリを使用する場合は、以下のパラメータをメモリの仕様にしたがって設定する。

- ADDSET : アドレス・セットアップタイム

- ADDHOLD : アドレス・ホールドタイム

- DATAST : データ・セットアップタイム

- ACCMOD : アクセスモード

同期メモリを使用する場合は、以下のパラメータを設定する。

- CLKDIV : クロック分周比

- DATLAT : データレイテンシ

また、NORフラッシュからプログラムを実行することもできる。

この場合、以下の手順が必要となる。

- ファームウェアを外部のNORフラッシュにロード

- この操作は、開発ツールチェーンのリンカファイルに対して、特別な設定が必要になる。

- 外部NORフラッシュの先頭アドレス(もしくは、NORフラッシュのメモリ空間のあるアドレス)を指定する必要がある。

- また、特別な外部NORフラッシュ用のプログラムローダも必要となる。

- ファームウェアの実行

- ファームウェアをNORフラッシュに書き込んだ後、FMCを設定して、外部NORフラッシュにジャンプして実行するような特別なプログラムを、

- 内部のフラッシュメモリにロードする。

FMC使用例2 : 非多重 / 非同期16ビットSRAMとの接続

SRAMとNORフラッシュは同じバンクを使用するが、バンクが同じでもメモリの種類によってプロトコルが変わるため、設定内容も異なる。

以下に、SRAMを制御するための設定例を示す。

他のパラメータは、全てクリア状態にする。

- バンクの使用を許可

- メモリタイプをSRAMに設定

- データバスを16ビットに設定(SRAMの仕様に依存)

- マルチプレックスをしない(SRAMの仕様に依存)

非同期NORフラッシュと同様に、以下のパラメータをSRAMの仕様にしたがって設定する。

- ADDSET : アドレス・セットアップタイム

- ADDHOLD : アドレス・ホールドタイム

- DATAST : データ・セットアップタイム

下図に、標準的なSRAMのアクセスタイミングを示す。

下図に、ハードウェアの接続例を示す。

QSPI (Quad SPIインタフェース)

QSPIインタフェースを持つ外部メモリであれば、STM32F745のQSPIモジュールを使用して接続できる。

QSPIのメモリマップドモードを使用する場合、外部メモリはアドレス空間(0x90000000台)に配置され、内部メモリのように扱うことができる。

下図に、マイコンの基礎 - Quad SPIの図を再掲する。