ATmega328のUSARTの使用方法(準備)

概要

PCとATmega328の間で、データの送受信を行う方法としてシリアル通信がある。

ATmega328では、シリアル通信が簡単にできるUSARTという機能があるので、USARTの知識と使用方法を記載する。

シリアル通信とUSART

シリアル通信で必要なもの

PCとATmega328の間で通信するために、両者を接続するものが必要である。

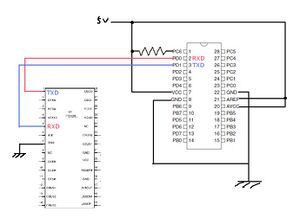

ここでは、FT232RL(USB−シリアル変換モジュール)を使用して、ATmega328のUSART機能でシリアル通信を行う。

ATmega328のシリアル通信で必要なもの

FT232RL(USB−シリアル変換モジュール)

USB miniBケーブル(FT232RLとPCを接続するケーブル)

FT232RLのドライバ(PCにインストールする)

FT232RLのドライバのインストール方法

- ドライバをFTDI社からダウンロードする。

- ダウンロードしたドライバを解凍する。

- FT232RLをPCに接続すると、ドライバを要求されるので、解凍したドライバのフォルダ(CDM ○○ WHQL Certified)を選択する。

- ドライバのインストールが完了する。

FT232RLは、USBポートから電源をとるか、外部から電源を供給するかをジャンパにより電源(Vcc)を選択することができる。

その他に、I/Oピンの電圧を3.3[V]またはVccかをジャンパにより選択することができる。

- ジャンパ1(J1)

- 1 - 2間をショート : I/Oの電圧を3.3[V]にする

- 2 - 3間をショート : I/Oの電圧をVccにする

- ジャンパ2(J2)

- 有り(ショート) : USBポートから電源を取る(Vcc = 5[V])

- 無し(オープン) : 外部から電源を取る(Vcc = 3.3 - 5[V])

USARTの設定

USARTのレジスタ設定

UCSRnA(USART Control and Status Register n A)は、シリアル通信の制御や状態を表すためのレジスタである。

| UCSRnA : USART制御/状態レジスタA(n : 0 or 1) | ||||||||

|---|---|---|---|---|---|---|---|---|

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 名前 | RXCn | TXCn | UDREn | FEn | DORn | UPEn | U2Xn | MPCMn |

- RXCn : USART受信完了フラグ

未読データがあるときに1がセットされる - TXCn : USART送信完了フラグ

新規データがないときに1がセットされる

送信完了割り込みを発生できる - UDREn : USART送信データレジスタ空きフラグ

送信バッファが新規データを受け取る準備ができたら1がセットされる

送信バッファ空き割り込みを発生できる - FEn : フレーミング異常フラグ

受信バッファ内の次の文字にフレームエラーが発生したときに1になる - DORn : データオーバーラン発生フラグ

データオーバーランを検出すると1になる

受信バッファが満杯のときに、新たにスタートビットを検出するとデータオーバーランが発生する - UPEn : パリティ誤りフラグ

受信バッファ内の次のフレームにパリティエラーが発生したときに設定される - U2Xn : 倍速許可

非同期通信のみ有効で、1を設定すると分周比を16から8にする

結果として、通信速度が2倍になる - MPCMn : 1を設定すると、マルチプロセッサ通信モードが有効になる

アドレス情報を含まない受信データが無視される

| UCSRnB : USART制御/状態レジスタB(n : 0 or 1) | ||||||||

|---|---|---|---|---|---|---|---|---|

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 名前 | RXCIEn | TXCIEn | UDRIEn | RXENn | TXENn | UCSZn2 | RXB8n | TXB8n |

- RXCIEn : 受信完了割り込み許可

UCSRnAの受信完了フラグ(RXCn)での割り込みを許可する - TXCIEn : 送信完了割り込み許可

UCSRnAの送信完了フラグ(TXCn)での割り込みを許可する - UDRIEn : 送信データレジスタ空き割り込み許可

UCSRnAのUDREnでの割り込みを許可する - RXENn : 受信許可

USART受信を許可する - TXENn : 送信許可

USART送信を許可する - UCSZn2 : データビット長選択2

USCRnCのUCSZn1とUCSZn0ビットと組み合わせたUCSZn2は、送受信フレームのデータのビット長を設定する - RXB8n : 9ビット長のデータを受信したときの9番目のビット

- TXB8n : 9ビット長のデータを送信するときの9番目のビット

UCSRnC(USART Control and Status Register n C)は、パリティやストップビットの設定を行うためのレジスタである。

| UCSRnC : USART制御/状態レジスタC(n : 0 or 1) | ||||||||

|---|---|---|---|---|---|---|---|---|

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 名前 | UMSELn 1 - 0 | UPMn 1 - 0 | USBSn | UCSZn 1 - 0 | UCPOLn | |||

- UMSELn 1 - 0 : USART動作選択

00(非同期動作)

01(同期動作)

10(予約)

11(マスターSPI) - UPMn 1 - 0 : パリティ選択

00(禁止)

01(予約)

10(偶数パリティ許可)

11(奇数パリティ許可) - USBSn : 送信時に挿入されるストップビットのビット数を指定する

0 : ストップビットは1ビット

1 : ストップビットは2ビット - UCSZn 1 - 0 : データビット長を選択

UCSZn2と組み合わせて使用する

000(5bit)

001(6bit)

010(7bit)

011(8bit)

111(9bit)

他は予約 - UCPOLn : クロック極性を選択する

1 : 同期モード

0 : 非同期モード

送信のタイミング

送信のタイミングは、UCSRnAレジスタの5ビット目であるUDREnに1がセットされると送信が有効になる。

例えば、下記のように記述すれば、送信が有効になると変数dataを送信することができる。

while(!(UCSR0A & 0b00100000)); // 送信が有効になるまで待つ

UDR0 = data; // データを送信する

受信のタイミング

受信のタイミングは、UCSRnAレジスタの7ビット目であるRXCnに1がセットされると受信は有効になる。

例えば、下記のように記述すれば、受信が有効になるまで待機し、データを受信することができる。

while(!(UCSR0A & 0b10000000)); // 受信が有効になるまで待つ

data = UDR0; // 受信したデータを格納する

ボーレートの設定

USARTのボーレートの設定は、UBRR0レジスタで設定する。(動的に設定することも可能)

UBRR0の値は、以下の式で計算することができる。

例えば、ATmega328のクロック周波数が1[MHz]、ボーレートを2400として通信する場合、UBRR0レジスタは下記の値となる。

FT232RLとATmega328の接続方法

USBポートから電源を取る場合は、以下のように回路を組めばシリアル通信ができる。