MSP430F149 - タイマ

概要

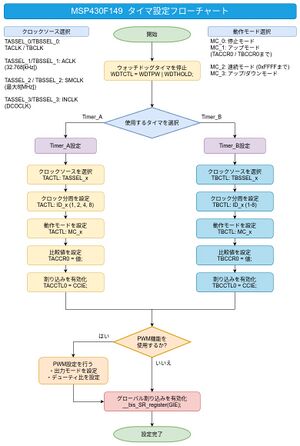

MSP430F149マイコンには、3つのタイマモジュールが搭載されている。

- Timer_A

- 16ビットのタイマ / カウンタ

キャプチャ / 比較レジスタを3つ備えている。 - Timer_Aモジュールは、3つのキャプチャ / 比較レジスタ (TACCR0、TACCR1、TACCR2) を備えている。

- 16ビットのタイマ / カウンタ

- Timer_B

- 16ビットのタイマ / カウンタ

キャプチャ / 比較レジスタを7つ備えている。 - Timer_Bモジュールは、7つのキャプチャ / 比較レジスタ (TBCCR0、TBCCR1、TBCCR2、TBCCR3、TBCCR4、TBCCR5、TBCCR6) を備えている。

- Timer_Bは、Timer_Aよりも高機能であり、より柔軟なタイマ動作が可能である。

- 16ビットのタイマ / カウンタ

- Watchdog Timer+

- ウォッチドッグタイマとして機能する16ビットのタイマである。

- また、インターバルタイマとしても使用可能である。

これらのタイマは、時間管理、イベントのスケジューリング、パルス幅変調 (PWM) の生成、外部信号のキャプチャ等、様々な用途に使用されている。

タイマの主な仕組みを以下に示す。

- カウント動作

- タイマはクロック信号に同期してカウント値を増加または減少させる。

- クロックソースは、内部クロック (SMCLK、ACLK)、外部クロック (TACLK、TBCLK) から選択できる。

- 動作モード

- タイマは、連続モード (カウンタが最大値に達すると0に戻る)、アップモード (カウンタが最大値に達すると停止)、アップ / ダウンモード (カウンタが最大値と0の間で増減を繰り返す) 等の動作モードを選択できる。

- 割り込み

- タイマは、カウンタが特定の値に達した場合や、キャプチャ / 比較イベントが発生した場合に割り込みを生成することができる。

- これにより、CPU負荷を最小限に抑えながらタイミングイベントを処理できる。

- キャプチャ / 比較機能

- タイマのキャプチャ / 比較レジスタを使用すると、外部信号のエッジ (立ち上がりまたは立ち下がり) を検出したり、PWM信号を生成したりすることができる。

- ウォッチドッグ機能

- ウォッチドッグタイマは、システムの異常動作を検出して、リセットを行うために使用される。

- 定期的にウォッチドッグタイマをリセットしないと、システムがリセットされる。

MSP430F149マイコンのタイマは、低消費電力動作とシンプルな設定が特徴である。

タイマの設定は、制御レジスタ (TACTLレジスタ、TACCTLxレジスタ、TBCTLレジスタ、TBCCTLxレジスタ) を通じて行う。

これらのレジスタを適切に設定することにより、目的に応じたタイマの動作を実現することができる。

Timer_Aモジュール

Timer_Aモジュールとは

MSP430F149マイコンには、Timer_Aという16ビットのタイマ / カウンタモジュールが搭載されている。

このTimer_Aモジュールは、3つのキャプチャ / 比較レジスタ (TACCR0、TACCR1、TACCR2) を備えており、それぞれが独立したタイマ機能として動作する。

複数の割り込みソース

- TACCR0

- タイマAのカウンタが、TACCR0レジスタの値に達した場合に発生する割り込み

- TACCR1

- タイマAのカウンタが、TACCR1レジスタの値に達した場合に発生する割り込み

- TACCR2

- タイマAのカウンタが、TACCR2レジスタの値に達した場合に発生する割り込み

- TAIFG

- タイマAの上記以外の割り込みフラグが設定された場合に発生する割り込み

TAIVレジスタの値と対応する割り込みソースを、以下に示す。

- 0x00

- 割り込みなし

- 0x02

- TACCR1

- 0x04

- TACCR2

- 0x0A

- TAIFG (カウンタオーバーフロー等)

PWM動作モードでは、TACCR0の値がPWM周期を決定、TACCR1の値がデューティ比を決定する。

TACCR1に関連する割り込みは、PWM周期ごとに発生する。

例えば、TAIVレジスタの値が0x02になる場合は、PWM周期ごとにTACCR1に関連する割り込みが発生していることを示す。

この割り込みを利用して、PWMのデューティ比を動的に変更することもできる。

TACCR0 / TACCR1 / TACCR2の違い

MSP430F149マイコンのTimer_Aモジュールには、3つのキャプチャ / 比較レジスタ (TACCR0、TACCR1、TACCR2) があり、それぞれが独立した機能を持つ。

これらのレジスタは基本的に同じ仕様であるが、いくつかの細かな違いがある。

- TACCR0

- キャプチャ / 比較レジスタ0を使用

- TACCR0レジスタは、タイマのカウント値を設定するために使用されることが多い。

- アップモード、アップ / ダウンモードで、カウンタの最大値を設定するために使用する。

- TACCR1

- キャプチャ / 比較レジスタ1を使用する。

- キャプチャモードと比較モードをサポート。

- 外部信号のエッジ検出やPWM生成に使用可能である。

- TACCR2

- キャプチャ / 比較レジスタ2を使用する。

- キャプチャモードと比較モードをサポート。

- 外部信号のエッジ検出やPWM生成に使用可能である。

主な違いは、TACCR0レジスタがタイマのカウント値を設定するために使用されることが多いのに対して、TACCR1レジスタとTACCR2レジスタはキャプチャや比較操作に使用されることが多い。

ただし、これらのレジスタは柔軟に使用できるため、用途に応じて各レジスタの役割を変更することができる。

また、TACCR1レジスタとTACCR2レジスタは、キャプチャモードと比較モードの両方をサポートしているが、TACCR0レジスタは主に比較モードで使用される。

それ以外の機能、such as動作モード、クロックソース、クロック分周、割り込み、出力モード等は、3つのレジスタで同じである。

したがって、TACCR0/1/2レジスタは、基本的には同じ仕様であるが、それぞれのキャプチャ / 比較レジスタの用途に応じて使い分けることができる。

Timer_A制御

下図に、Timer_Aモジュールのブロック図を示す。

動作モード

- アップモード

- カウンタが

0からTACCR0レジスタに設定した値まで増加して、TACCR0レジスタに設定した値に達するとカウンタが0に戻る。

- カウンタが

- 連続モード

- カウンタが

0からFFFFhまで増加して、FFFFhに達すると0に戻る。

- カウンタが

- アップ / ダウンモード

- カウンタが

0からTACCR0レジスタに設定した値まで増加して、TACCR0レジスタに設定した値に達するとTACCR0レジスタの値から0まで減少する。

- カウンタが

クロックソース

- TACLK

- 外部クロック信号を使用する。

- ACLK

- 補助クロック (32.768[kHz]) を使用する。

- SMCLK

- サブメインクロック (最大8[MHz]) を使用する。

- INCLK

- 内部クロック (DCOCLK) を使用する。

クロック分周

1、2、4、8分周が可能である。

割り込み

- TACCR0との比較一致割り込み (CCIFG)

- TACCR1との比較一致割り込み (CCIFG)

- TACCR2との比較一致割り込み (CCIFG)

- カウンタオーバーフロー割り込み (TAIFG)

出力モード

- 比較モード

- TACCRxレジスタとの比較一致に基づいて出力信号の状態を変更する。

- セット/リセットモード

- TACCRxレジスタとの比較一致でセット、TACCR0との比較一致でリセットする。

- トグル/リセットモード

- TACCRxレジスタとの比較一致でトグル、TACCR0との比較一致でリセットする。

- セット モード

- TACCRxレジスタとの比較一致で出力をセットする。

- トグルモード

- TACCRxレジスタとの比較一致で出力信号をトグルする。

- リセット/セットモード

- TACCRxレジスタとの比較一致でリセット、TACCR0との比較一致でセットする。

- リセットモード

- TACCRxレジスタとの比較一致で出力をリセットする。

キャプチャモード

- 立ち上がりエッジ

- 入力信号の立ち上がりエッジでキャプチャする。

- 立ち下がりエッジ

- 入力信号の立ち下がりエッジでキャプチャする。

- 両エッジ

- 入力信号の両エッジでキャプチャする。

Timer_Bモジュール

Timer_Bモジュールとは

MSP430F149マイコンには、Timer_Bという16ビットのタイマ / カウンタモジュールが搭載されている。

このTimer_Bモジュールは、7つのキャプチャ / 比較レジスタ (TBCCR0、TBCCR1、TBCCR2、TBCCR3、TBCCR4、TBCCR5、TBCCR6) を備えており、Timer_Aよりも高機能である。

Timer_Bは、Timer_Aと同様の機能を持ちながら、より多くのキャプチャ / 比較レジスタを備えているため、複雑なタイミング制御やPWM生成に適している。

Timer_Bの主な特徴

- 7つのキャプチャ / 比較レジスタ

- TBCCR0からTBCCR6までの7つのレジスタを使用可能

- ダブルバッファリング

- Timer_Bは、ダブルバッファリング機能をサポートしており、グリッチフリーなPWM更新が可能

- グループ化されたチャネル

- 複数のキャプチャ / 比較チャネルをグループ化して、同期動作が可能

複数の割り込みソース

- TBCCR0

- タイマBのカウンタが、TBCCR0レジスタの値に達した場合に発生する割り込み

- TBCCR1-TBCCR6

- タイマBのカウンタが、TBCCR1からTBCCR6レジスタの値に達した場合に発生する割り込み

- TBIFG

- タイマBの上記以外の割り込みフラグが設定された場合に発生する割り込み

TBIVレジスタの値と対応する割り込みソースを、以下に示す。

- 0x00

- 割り込みなし

- 0x02

- TBCCR1

- 0x04

- TBCCR2

- 0x06

- TBCCR3

- 0x08

- TBCCR4

- 0x0A

- TBCCR5

- 0x0C

- TBCCR6

- 0x0E

- TBIFG (カウンタオーバーフロー等)

Timer_B制御

下図に、Timer_Bモジュールのブロック図を示す。

動作モード

- アップモード

- カウンタが

0からTBCCR0レジスタに設定した値まで増加して、TBCCR0レジスタに設定した値に達するとカウンタが0に戻る。

- カウンタが

- 連続モード

- カウンタが

0からFFFFhまで増加して、FFFFhに達すると0に戻る。

- カウンタが

- アップ / ダウンモード

- カウンタが

0からTBCCR0レジスタに設定した値まで増加して、TBCCR0レジスタに設定した値に達するとTBCCR0レジスタの値から0まで減少する。

- カウンタが

クロックソース

- TBCLK

- 外部クロック信号を使用

- ACLK

- 補助クロック (32.768[kHz]) を使用

- SMCLK

- サブメインクロック (最大8[MHz]) を使用

- INCLK

- 内部クロック (DCOCLK) を使用

クロック分周

Timer_Bでは、1、2、3、4、5、6、7、8分周が可能である。

Timer_Aと異なり、より柔軟な分周設定が可能である。

割り込み

- TBCCR0との比較一致割り込み (CCIFG)

- TBCCR1-TBCCR6との比較一致割り込み (CCIFG)

- キャプチャ割り込み (CCIFG)

- カウンタオーバーフロー割り込み (TBIFG)

出力モード

- 比較モード

- TBCCRxレジスタとの比較一致に基づいて出力信号の状態を変更する。

- セット/リセットモード

- TBCCRxレジスタとの比較一致でセット、TBCCR0との比較一致でリセットする。

- トグル/リセットモード

- TBCCRxレジスタとの比較一致でトグル、TBCCR0との比較一致でリセットする。

- セット モード

- TBCCRxレジスタとの比較一致で出力をセットする。

- トグルモード

- TBCCRxレジスタとの比較一致で出力信号をトグルする。

- リセット/セットモード

- TBCCRxレジスタとの比較一致でリセット、TBCCR0との比較一致でセットする。

- リセットモード

- TBCCRxレジスタとの比較一致で出力をリセットする。

キャプチャモード

- 立ち上がりエッジ

- 入力信号の立ち上がりエッジでキャプチャ

- 立ち下がりエッジ

- 入力信号の立ち下がりエッジでキャプチャ

- 両エッジ

- 入力信号の両エッジでキャプチャ

Watchdog Timer+

MSP430F149マイコンには、Watchdog Timer+と呼ばれる16ビットのタイマモジュールが搭載されている。

Watchdog Timer+は、システムの異常動作を検出して、リセットを行うために使用される。

また、インターバルタイマとしても使用可能である。

Watchdog Timer+の設定は、WDTCTLレジスタ (ウォッチドッグタイマ制御レジスタ) を使用して行う。

このレジスタを適切に設定することにより、目的に応じたWatchdog Timer+の動作を実現することができる。

ウォッチドッグ機能を使用する場合は、定期的にWDTCTLレジスタに特定の値を書き込んでウォッチドッグをリセットする必要がある。

インターバルタイマとして使用する場合は、WDTCTLレジスタを設定して割り込みを有効にすることにより、一定間隔でイベントを生成できる。

Watchdog Timer+は、システムの信頼性を向上させるための重要な機能であり、適切に設定・使用することが重要である。

ウォッチドッグ機能

- システムの異常動作を検出して、リセットを行う。

- ウォッチドッグタイマをリセットしないと、システムがリセットされる。

- ウォッチドッグ機能は、ソフトウェアの無限ループやハングアップから復旧するための安全装置である。

インターバルタイマ機能

- 一定間隔でイベントを生成するためのタイマとして使用可能である。

- 割り込み要求を生成して、特定のタスクを実行するトリガーとして使用する。

クロックソース

- ACLK

- 補助クロック (32.768[kHz]) を使用する。

- SMCLK

- サブメインクロック (最大8[MHz]) を使用する。

クロック分周

の分周が可能である。

1、2、4、8、16、32、64

ウォッチドッグ間隔

- クロックソースとクロック分周の設定により、ウォッチドッグ間隔を調整可能

- 最短で数msから最長で数秒までの間隔を設定可能

割り込み

- ウォッチドッグタイマの割り込み (WDTIFG) が生成可能である。

- 割り込みを使用して、特定のタスクを実行したり、システムの状態を監視したりすることが可能である。

ウォッチドッグ動作モード

- ウォッチドッグモード

- システムリセットを行うためのモード

- インターバルタイマモード

- 一定間隔で割り込みを生成するためのモード

Timer_A / Timer_Bの設定

Timer_A / Timer_Bの使用

サンプルコード

以下の例では、Timer_A TACCR0の比較一致割り込み (TACCR0の割り込みサービスルーチン) により、LEDを1秒ごとにトグルしている。

Timer_Aの使用

- TACCR0の比較一致割り込みを有効する。

- TACCR0に を設定して、1秒間隔で割り込みが発生するように設定する。 (ACLKは、32.768[kHz])

- Timer_AのクロックソースをACLKに設定して、アップモードで動作させる。

#include <msp430.h>

#define LED_PIN BIT0 // LEDが接続されているピン (例: P1.0)

int main(void)

{

WDTCTL = WDTPW | WDTHOLD; // ウォッチドッグタイマを停止

P1DIR |= LED_PIN; // LEDピンを出力に設定

// Timer_Aの設定

TACCTL0 = CCIE; // TACCR0の比較一致割り込みを有効化

TACCR0 = 32768 - 1; // 1秒間隔 (ACLK = 32.768[kHz])

TACTL = TASSEL_1 | MC_1; // ACLKを選択して、アップモード

// 低電力モード3 (LPM3), 割り込みを有効化

__bis_SR_register(LPM3_bits | GIE);

// 空の操作 (コンパイラの最適化を防ぐため)

__no_operation();

}

// Timer_A TACCR0の割り込みサービスルーチン

#pragma vector=TIMERA0_VECTOR

__interrupt void Timer_A0_ISR(void)

{

P1OUT ^= LED_PIN; // LEDの状態を切り替え

}

Timer_Bの使用

Timer_Bを使用する場合、割り込みベクタ名はTIMERB0_VECTORとなる。

#include <msp430.h>

#define LED_PIN BIT0 // LEDが接続されているピン (例: P1.0)

int main(void)

{

WDTCTL = WDTPW | WDTHOLD; // ウォッチドッグタイマを停止

P1DIR |= LED_PIN; // LEDピンを出力に設定

// Timer_Bの設定

TBCCTL0 = CCIE; // TBCCR0の比較一致割り込みを有効化

TBCCR0 = 32768 - 1; // 1秒間隔 (ACLK = 32.768[kHz])

TBCTL = TBSSEL_1 | MC_1; // ACLKを選択して、アップモード

// 低電力モード3 (LPM3), 割り込みを有効化

__bis_SR_register(LPM3_bits | GIE);

// 空の操作 (コンパイラの最適化を防ぐため)

__no_operation();

}

// Timer_B TBCCR0の割り込みサービスルーチン

#pragma vector=TIMERB0_VECTOR

__interrupt void Timer_B0_ISR(void)

{

P1OUT ^= LED_PIN; // LEDの状態を切り替え

}